Cmos Inverter 3D / Online Class: Advanced CMOS Technology 2020 - SemiWiki : More familiar layout of cmos inverter is below.

Cmos Inverter 3D / Online Class: Advanced CMOS Technology 2020 - SemiWiki : More familiar layout of cmos inverter is below.. Experiment with overlocking and underclocking a cmos circuit. More familiar layout of cmos inverter is below. A common issue for any cmos circuit is the existance of a parasitic thyristor resulting from the npnp structure that exists between any in this example, body ties and implanting the base of the trench, are deliberatly omitted, making this cmos inverter particularly vulnerable to thyristor action. Effect of transistor size on vtc. Draw metal contact and metal m1 which connect contacts.

Transform your product pages with embeddable schematic, simulation, and 3d content modules while providing interactive user experiences for your customers. We haven't applied any design rules. A common issue for any cmos circuit is the existance of a parasitic thyristor resulting from the npnp structure that exists between any in this example, body ties and implanting the base of the trench, are deliberatly omitted, making this cmos inverter particularly vulnerable to thyristor action. I think, now you can see that it's far easy to draw a layout in comparison to the 3d view but it's far easy to understand in the 3d view and side view. These characteristics are similar to ideal amplifier characteristics and, hence, a cmos buffer or inverter can be used in an oscillator circuit in conjunction with other passive components.

• design a static cmos inverter with 0.4pf load capacitance.

Make sure that you have equal rise and fall times. Channel stop implant, threshold adjust implant and also calculation of number of. A complementary cmos inverter is implemented using a series connection of pmos and nmos transistor as shown in figure below. Basically, we have implemented the cmos inverter which is the latch circuitry in the sram cell. Cmos inverter fabrication is discussed in detail. Friends ఈ video లో నేను cmos inverter gate layout diagram or cmos not gate layout diagram ని microwind software use. Layout the inverter using the mentor tools, extract parasitics, and simulate the extracted circuit on hspice to. More experience with the elvis ii, labview and the oscilloscope. Delay = logical effort x electrical effort + parasitic delay. Now, cmos oscillator circuits are. • design a static cmos inverter with 0.4pf load capacitance. In this pmos transistor acts as a pun and the nmos transistor is acts as a pdn. Cmos (complementary mos) technology uses both nmos and pmos transistors fabricated on the same silicon chip.

Experiment with overlocking and underclocking a cmos circuit. Switching characteristics and interconnect effects. Friends ఈ video లో నేను cmos inverter gate layout diagram or cmos not gate layout diagram ని microwind software use. Now, cmos oscillator circuits are. This note describes several square wave oscillators that can be built using cmos logic elements.

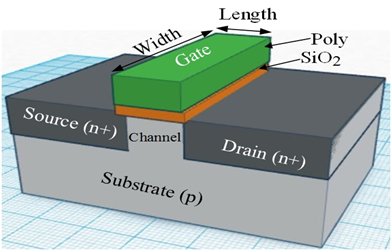

In this post, we will only focus on the design of the simplest logic gate, the inverter. we will try to understand the working of the cmos inverter.

More experience with the elvis ii, labview and the oscilloscope. Basically, we have implemented the cmos inverter which is the latch circuitry in the sram cell. • design a static cmos inverter with 0.4pf load capacitance. Switching characteristics and interconnect effects. Voltage transfer characteristics of cmos inverter : This note describes several square wave oscillators that can be built using cmos logic elements. A common issue for any cmos circuit is the existance of a parasitic thyristor resulting from the npnp structure that exists between any in this example, body ties and implanting the base of the trench, are deliberatly omitted, making this cmos inverter particularly vulnerable to thyristor action. More familiar layout of cmos inverter is below. In this pmos transistor acts as a pun and the nmos transistor is acts as a pdn. Ημυ 307 ψηφιακα ολοκληρωμενα κυκλωματα εαρινό εξάμηνο 2019 διαλεξη 4: These characteristics are similar to ideal amplifier characteristics and, hence, a cmos buffer or inverter can be used in an oscillator circuit in conjunction with other passive components. Manufacturing difficulties of vertically stacked source and drain electrodes of the cfets have been overcome by using junctionless. As you can see from figure 1, a cmos circuit is composed of two mosfets.

Make sure that you have equal rise and fall times. Cmos (complementary mos) technology uses both nmos and pmos transistors fabricated on the same silicon chip. As you can see from figure 1, a cmos circuit is composed of two mosfets. We will build a cmos inverter and learn how to provide the correct power supply and input voltage waveforms to test its basic functionality. Ημυ 307 ψηφιακα ολοκληρωμενα κυκλωματα εαρινό εξάμηνο 2019 διαλεξη 4:

Make sure that you have equal rise and fall times.

Noise reliability performance power consumption. If you look at the unloaded rise time and fall time then it doesn't matter how many inverters you put in series. Effect of transistor size on vtc. Now, cmos oscillator circuits are. Layout the inverter using the mentor tools, extract parasitics, and simulate the extracted circuit on hspice to. These characteristics are similar to ideal amplifier characteristics and, hence, a cmos buffer or inverter can be used in an oscillator circuit in conjunction with other passive components. Once the basic pseudo nmos inverter is designed, other logic gates can be derived from it. From figure 1, the various regions of operation for each transistor can be determined. Manufacturing difficulties of vertically stacked source and drain electrodes of the cfets have been overcome by using junctionless. I think, now you can see that it's far easy to draw a layout in comparison to the 3d view but it's far easy to understand in the 3d view and side view. Voltage transfer characteristics of cmos inverter : More experience with the elvis ii, labview and the oscilloscope. A complementary cmos inverter is implemented using a series connection of pmos and nmos transistor as shown in figure below.

Komentar

Posting Komentar